# **SIMULATION OF THREE PHASE 5- LEVEL** CASCADED H-BRIDGE INVERTER FED BLDC

<sup>1</sup>J. Srinivas Rao, <sup>2</sup>Dr.T. Suresh Kumar

<sup>1</sup>Assistant Professor & Research Scholar, KLEF, <sup>2</sup>Professor <sup>1</sup>Electrical and Electronics Engineering <sup>1</sup>Anurag Engineering College, Kodad, India

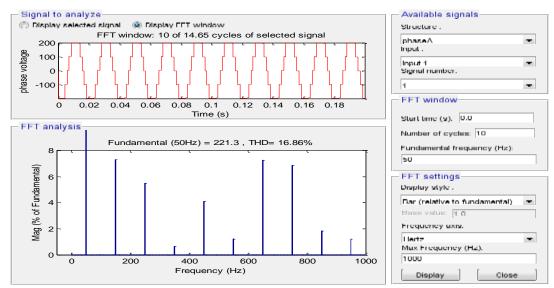

Abstract : This paper presents performance of three phase five level Cascaded H-Bridge multi level inverter fed BLDC motor. The output phase voltage of this topology is synthesized by the addition of the voltages that are generated by different modules. The total harmonic distortion of the output voltage is calculated. The converter fed BLDC motor is extensively simulated in MATLAB/Simulink.

Index Terms - Cascaded H-Bridge (CHB), BLDC Motor, total harmonic distortion (THD)

#### I. INTRODUCTION

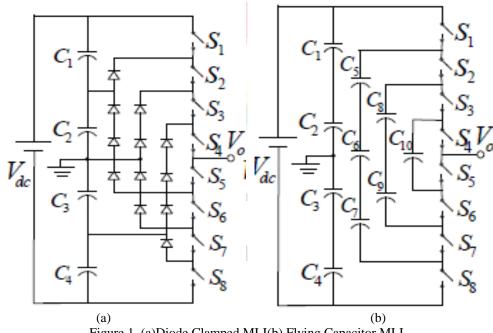

Multilevel inverters have been in the center of focus for the past decades because of interesting features such as improved output voltage quality, ability to operate in high voltage/power condition, better electromagnetic compatibility etc. They have made their way successfully into the industry and therefore can be considered mature and proven technology. The basic principle of the multilevel inverters is to divide the operating voltage of the inverter between power electronic switches so that low-voltage switches can be used to process high-voltage outputs. This capability has made the multilevel inverters suitable for high and medium voltage/power applications such as large motor drives, flexible AC transmission systems, VAR compensation and many other applications. On the other hand, increasing the number of inverter levels leads to achieving high-quality output voltages at low switching frequencies. The hard ware circuitry required is more as number of levels are increased. Many topologies for multilevel inverters were proposed; the most popular being the diode-clamped [1], [2], H-bridge [4] structures Diode clamped and Flying capacitor MLIs require complex circuitry as flying capacitor [3], and cascaded number of levels increase. â.

Figure 1. (a)Diode Clamped MLI(b) Flying Capacitor MLI

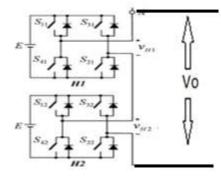

### II. Cascade H-bridge multilevel inverter:

Multilevel cascade inverter is used to eliminate the bulky transformers required in case of a conventional multi-phase inverter, clamping diodes required in case of the diode-clamped inverter and flying capacitors required in case of flying capacitor inverter. The numbers of switches required for Cascaded H-Bridge(CHB) Multilevel inverter are less in each level. H-Bridge consists of switches and capacitors combination. Each H-Bridge is supplied by separate DC source and number of such H-Bridges is connected in series to get multi level output voltage. Each H-Bridge provides three voltage levels like 0,+Vdc,-Vdc. Equation for level of output voltage is

$$V_{level} = 2 * N + 1$$

## Where N= Number of DC Sources

The advantage of this type of multi level inverter is that The price and weight of the inverter are less than those of the two inverters. Softswitching is possible by the some of the new switching methods.

Figure 2: Single phase 5-level cascaded H-Bridge Inverter

Two H-Bridge H1 and H2 consists of a separate DC source as shown in Fig. Let the output of H1be denoted as  $E_1$ , the output of H2 be denoted as  $E_2$ . Hence the total output voltage is given by

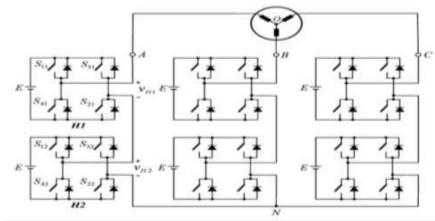

Figure 3: three phase 5-level cascaded H-Bridge Inverter fed BLDC motor

#### **III. SIMULATION RESULTS:**

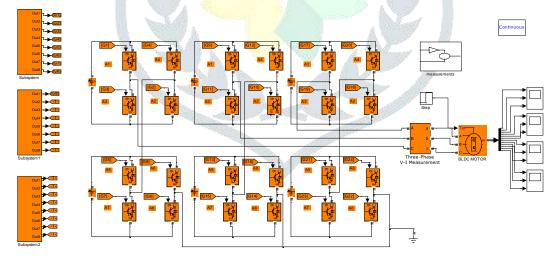

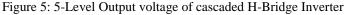

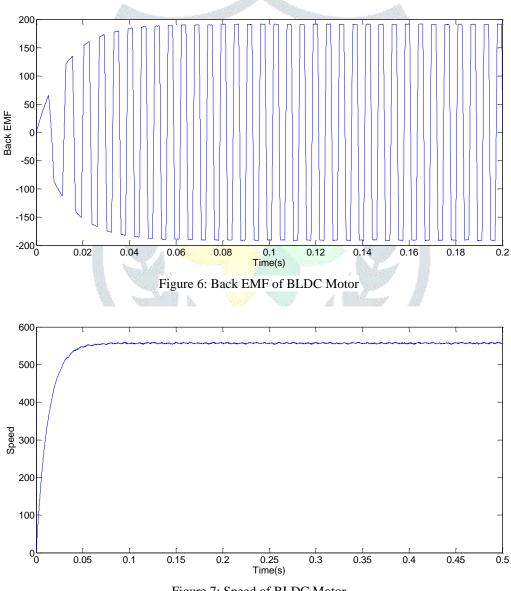

Three phase five level cascaded H bridge MLI fed BLDC drive is simulated in MATLAB/Simulink environment.

Figure 4: Simulink diagram of three phase 5-level cascaded H-Bridge Inverter fed BLDC motor

#### Figure 7: Speed of BLDC Motor

#### **IV. CONCLUSION**

Simulation of three phase 5-level CHB inverter fed BLDC motor drive is performed in MATLAB/Simulink environment. The THD for output voltage of inverter, Back EMF of BLDC Motor is calculated. The THD can be reduced by increasing number of levels of voltage.

#### **REFERANCES:**

[1] M. Fracchia, T. Ghiara, M. Marchesoni, and M. Mazzucchelli, "Optimized modulation techniques or the gemeralized N-level converter," *in proc. IEEE power electronics specialist conf*, 1205-1213, *Madrid*, Spain, 1992.

[2] K. A. Corzine and J. R. Baker, "Reduced parts-count multilevel retifiers," "*IEEE Trans. Ind. Electron.*" vol.49, no.3, pp. 766-774, Aug. 2002.

[3] ] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," "*IEEE Trans. Ind. Applica*," vol. 37, pp. 611-618, Mar./April 2004.

[4] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: a competitive solution for high-power applications," "*IEEE Trans. Ind. Applica*," vol. 36, pp.

834-841, May/June 2000.

[5] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications,"

[6] Multistring five-level inverter with novel PWM control scheme for pv application.